第七章 常用时序逻辑部件

这一章主要是介绍常用的时序逻辑功能部件。如计数器、移位寄存器的分析与设计方法以及集成计数器、集成移位寄存器的原理及应用。它是本课程的重点内容之一,我们一定要掌握好!

在学习时要注意同步、异步计数器和移位寄存器的工作原理及设计方法;同步式集成计数器T214、异步式集成计数器T210以及集成移位寄存器T454的工作原理及应用。

在学习是我们把这一章的内容共分为三节,它们分别是:

§1.计数器

§2.寄存器与移位寄存器

§3.序列信号发生器

§7、1 计数器

累计输入脉冲的个数的逻辑电路称为计数器。它的作用有:累计输入脉冲的个数;对输入脉冲信号进行分频;构成其它时序电路。

计数器的分类:

按进位模数分为模2计数器和非模2计数器。

按进位模数分为模2计数器和非模2计数器。

进位模是计数器所经历的独立状态的总数,也就是进位制数。

模2计数器就是进位模为2n的计数器。其中n为触发器的级数;非模2计数器就是进位模非2n的计数器。

按计数脉冲的输入方式分为同步计数器和异步计数器。

按计数脉冲的输入方式分为同步计数器和异步计数器。

同步计数器是相应的触发器的计数脉冲也相同,使相应的触发器同时翻转。异步计数器是相应的触发器的计数脉冲不相同,并且不同时翻转。

按计数增减趋势分为递增计数器、递减计数器和双向计数器。

按计数增减趋势分为递增计数器、递减计数器和双向计数器。

递增计数器是每来一个时钟脉冲触发器的组成状态按二进制代码规律增加,递减计数器就是按二进制代码规律减少。双向计数器是可增可减,由控制端来决定。

按电路集成度分为小规模集成计数器和中规模集成计数器。

按电路集成度分为小规模集成计数器和中规模集成计数器。

一:同步计数器的分析与设计

在设计同步计数器是由于已经明确了状态数、状态代码和状态迁移关系,所以不需要制作原始状态图、状态化简和状态分配。

1.二进制计数器的设计

模为2的同步计数器称为二进制计数器,它的特点是没有多余状态,触发器的利用率高。它通常是采用自然二进制编码。

例1.设计一个三位二进制同步递增计数器.

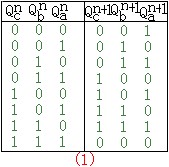

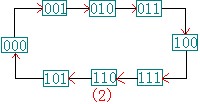

三位二进制的进位模数为23=8,它的状态表为:如图(1)所示.状态迁移图为:如图(2)所示

将现态QCn、QBn、QAn作为输入,次态QCn+1、QBn+1、QAn+1作为输出,通过卡诺图可得出各触发器的次态方程为:

QCn+1=QAnQBnQCn+QAnQCn+QBnQCn=QAnQBnQC+QAnQBnQC

QBn+1=QAnQBn+QAnQBn

QAn+1=QAn

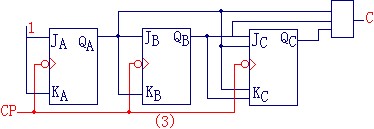

把求得的次态方程与选用触发器的特征方程作比较,求得各触发器的激励函为:

它的逻辑电路图为:如图(3)所示

位数增多的二进制计数器的设计可按以上方法进行,当位数>5时,就不能用上面的方法了(卡诺图不易制),从上面的例子我们可以看出:低级触发器除外,每一位触发器的J,K激励函数都是由它的低位各触发器原码相与而成.由此就可以设计更多位的二进制计数器了.

二进制的减法计数器的设计方法与加法相似,只不过状态迁移图不同.

[1] [2] [3] [4] [5] [6] [7] 下一页