| 74hc138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码之逆过程。译码器之输入是n位二值代码,输出是m个表征代码原意之状态信号(或另一种代码)。一般情况下有m小于等于2之n次方,即译码器输入线比输出线要少。译码器按其功能可分为三大类: (1)变量译码器:将输入之二进制代码还原为原始输入信号。例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1) (2)代码变换译码器:用于将一个数据之不同代码之间之相互转换。例如二-十进制译码器可将8421码转换为十个状态。 (3)显示译码器:将数字、文字或符号之代码还原成相应之数字、文字、符号并显示出来之电路 74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。 hc138 作用原理于高性能之存贮译码或要求传输延迟时间短之数据传输系统,在 高性能存贮器系统中,用这种译码器可以提高译码系统之效率。将快速赋能电路用于高速存贮器时,译码器之延迟时间和存贮器之赋能时间通常小于存贮器之典型存取时间,这就是说由肖特基钳位之系统译码器所引起之有效系统延迟可以忽略不计。HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个

低电平输出。两个低电平有效之赋能输入端和一个高电平有效之赋能输入端减少了扩展所需要之外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。在解调器应用中,赋能输入端可用作数据输入端。 | 74HC138 74HCT138 T1TRUTH TABLE真值功能表 | | INPUTS 输入 | Outputs输出 | | ENABLE 使能 | ADDRESS地址 | | E3 | E2 | E1 | A2 | A1 | A0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | | X | X | H | X | X | X | H | H | H | H | H | H | H | H | | L | X | X | X | X | X | H | H | H | H | H | H | H | H | | X | H | X | X | X | X | H | H | H | H | H | H | H | H | | H | L | L | L | L | L | L | H | H | H | H | H | H | H | | H | L | L | L | L | H | H | L | H | H | H | H | H | H | | H | L | L | L | H | L | H | H | L | H | H | H | H | H | | H | L | L | L | H | H | H | H | H | L | H | H | H | H | | H | L | L | H | L | L | H | H | H | H | L | H | H | H | | H | L | L | H | L | H | H | H | H | H | H | L | H | H | | H | L | L | H | H | L | H | H | H | H | H | H | L | H | | H | L | L | H | H | H | H | H | H | H | H | H | H | L | | CD74HC238, CD74HCT238 T1TRUTH TABLE真值表 | | INPUTS 输入 | Outputs输出 | | ENABLE 使能 | ADDRESS地址 | | E3 | E2 | E1 | A2 | A1 | A0 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | | X | X | H | X | X | X | L | L | L | L | L | L | L | L | | L | X | X | X | X | X | L | L | L | L | L | L | L | L | | X | H | X | X | X | X | L | L | L | L | L | L | L | L | | H | L | L | L | L | L | H | L | L | L | L | L | L | L | | H | L | L | L | L | H | L | H | L | L | L | L | L | L | | H | L | L | L | H | L | L | L | H | L | L | L | L | L | | H | L | L | L | H | H | L | L | L | H | L | L | L | L | | H | L | L | H | L | L | L | L | L | L | H | L | L | L | | H | L | L | H | L | H | L | L | L | L | L | H | L | L | | H | L | L | H | H | L | L | L | L | L | L | L | H | L | | H | L | L | H | H | H | L | L | L | L | L | L | L | H |

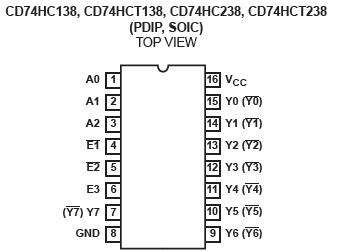

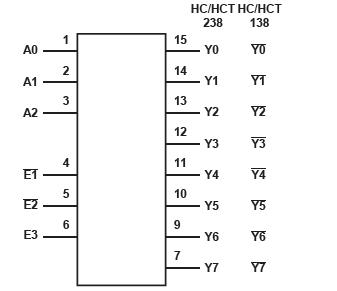

图1 引脚图 图2 功能图

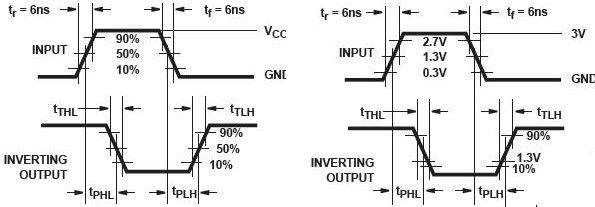

图3 测试电路和波形 应用电路: |

图4 舞台发光二极管灯光 |  | 图5 可编程时钟定时器电路 |

由上表可见74HC138译码器输出低电平有效。为增加译码器功能,除三个输入端C、 B、 A 外,还设置了G1、/G2A,/G2B,使译码器具有较强之抗干扰能力且便于扩展。

当G1=0时,不管其他输入如何,电路输出均为“1”,即没有译码输出;只有当G1=1,且/G2A=/G2B=0时,译码器才处于允许工作状态,输出与输入二进制码相对应,如 CBA=110 时,Y6输出低电平。